大芯片的“破局”与“困局”:面板级封装的经济远景与工程真相

将半导体封装在巨大的矩形面板(而非圆形晶圆)上加工的设想已流传多年。它曾多次引起关注,又因实际困难超过预期收益而几度沉寂。但现在,实现这一目标的推力正达到顶峰。

随着 AI 加速器和高性能计算(HPC)封装的体积不断增大,晶圆级加工的经济性在巨大的面积需求下开始捉襟见肘。行业与其说是主动选择面板,不如说是被经济和技术趋势推向了面板。

Lam Research 全球产品组高级副总裁 Sesha Varadarajan 在近期演讲中表示:“封装技术已与前端工艺并驾齐驱,成为推动芯片持续微缩不可或缺的核心力量。先进封装将所有芯片类型整合在一起,而封装的缩放不仅是为了提高 I/O 密度,也是为了在未来融入包括硅光子在内的新型架构。”

迈向大尺寸的理由

面板级加工的经济逻辑十分清晰:对于昂贵的大尺寸 AI 和 HPC 封装而言,成本的重灾区已不再是芯片本身,而是围绕芯片构建的基板与组装设施。由于晶圆加工单次产出有限,且随着模块尺寸逼近甚至突破光刻掩模极限,这种产出约束所带来的成本溢价正变得愈发不可承受。

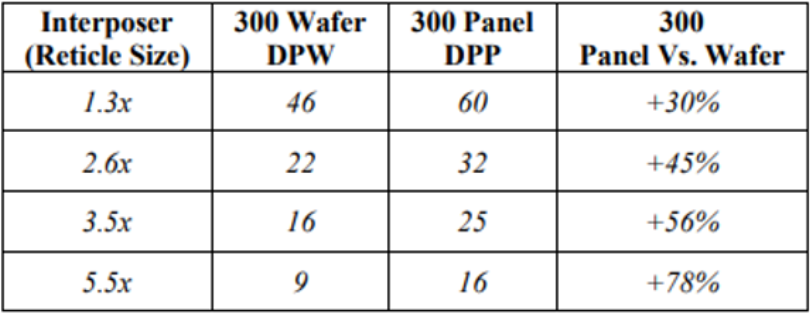

随着封装尺寸增大,每片 300mm 晶圆能容纳的单元变少,边缘损失增加,每个加工步骤的成本被分摊到更少的待售封装上。结果就是:随着模块面积扩大,晶圆级经济效益持续恶化。面板加工通过将圆形晶圆中介层替换为面积大出数倍的矩形基板,增加了单次运行的产量,从而更有效地分摊固定成本。

SavanSys 总裁 Amy Lujan 在近期演示中指出:“普遍共识是我们正处于面板扇出型封装(Panel Fan-out)的第二波浪潮。最初的兴趣集中在标准扇出方式,即在大面板上加工相似的小封装;而现在,HPC 和 AI 芯片的需求促使大家对更先进工艺流程下的面板扇出产生浓厚兴趣。”

Lujan 的成本模型重点探讨了 310mm x 310mm 这一规格。这一‘过渡尺寸’既显著超越了传统晶圆的尺度,又避开了激进迈向超大面板格式所带来的极端技术风险。随着封装复杂度飙升,此类中间规格正受到业界的严正审视——这恰恰反映出面板级工艺的经济吸引力已今非昔比。对于下一代 AI 加速器而言,由于单颗封装成本极高,哪怕单次产出率仅有微幅提升,也足以支撑起对新工艺开发的大手笔投入。”

“然而,经济账算得通,并不代表技术路走得顺。业界正愈发清醒地意识到:面板级加工面临的是一种‘复合型挑战’,单凭晶圆级的技术积淀,根本无法简单地‘等比推演’出面板级的解决方案。

玻璃的“极限承压”

作为面板级基板的头号候选材料,玻璃备受瞩目。它的热膨胀系数(CTE)能与硅近乎完美匹配,表面平整度足以支撑超细间距加工,且其透明特性极利于紫外线或激光解键合工艺。相比之下,传统的有机基板在尺寸稳定性、高频介质损耗以及大尺寸翘曲方面的缺陷早已众所周知,这使得玻璃成为极具吸引力的替代方案。

然而,玻璃的硬伤在于其脆性,且这种脆性并不会随着基板尺寸的扩大而变得温顺。虽然玻璃的大多数失效模式在理论上已被破解,但在实践中却极难根除。当工艺转向面板级时,这一矛盾愈发尖锐:边缘长度大幅增加,搬运应力成倍增长,且下游的每一个工序都在被动承受前序工序累积下来的机械损伤“前科”。

起始玻璃材料的表面质量,其影响权重往往被低估了。 原料准备或早期的研磨抛光中引入的微裂纹,会沦为后续工艺中极易被“撕开”的应力集中点。湿法刻蚀、热循环或机械搬运都可能诱发或加剧这些裂纹,而此类损伤往往像隐疾一样潜伏在工艺流深处,直到后期才爆发为毁灭性的失效。

Plan Optik AG 销售主管 Jonas Discher 指出:“如果初始表面就带伤,那么整个下游工艺都将笼罩在破碎的阴影下。微裂纹将直接转化为良率损失和可靠性隐患。”

尺寸效应进一步放大了这种忧虑,且很难通过单纯的工程手段规避。那些在 300mm 晶圆上尚且可控的微裂纹,到了 310mm 甚至更大的面板上就变成了致命变量——边缘越长,接触摩擦的机会就越多,加工应力会被分布在一个更大、且均匀性更差的区域。

裂纹不仅存在于表面,更深入玻璃内部。穿孔玻璃通孔(TGV)是实现电气互连的核心,但填充其中的铜与玻璃在热循环下的行为迥异。Applied Materials 的专家 Poulomi Mukherjee 拆解了这一“连环失效”过程:

“加热时,由于热膨胀失配,铜膨胀更剧烈,在通孔凹陷处形成应力集中并诱发裂纹。而在冷却过程中,收缩的铜又会反过来拉扯玻璃产生张应力,最终导致裂纹呈环向扩散。”

理解了失效机理,才可能从材料层面破局。Applied Materials 通过对衬垫材料(Liner)的模量与 CTE 进行反复交叉测试发现:单纯的高 CTE 衬垫无法解决失配;低 CTE 但高模量的衬垫则因太硬而无法吸收应变能。最终的“标准答案”是低 CTE 与低模量的结合。 这种材料既能补偿膨胀差异,又能像缓冲垫一样吸收应变。

模拟结果显示,这种优化后的衬垫能将关键点的应力降低 60%,同时还改善了种子层对玻璃侧壁的附着力。这揭示了面板级开发的一个通用特征:它不再是孤立的封装问题,而是材料特性、沉积设备与工艺时序的深度“协同工程”。

甚至连临时载板(Carriers)也带来了新难题。从经济角度看,玻璃载板循环使用极具诱惑力,但其实际表现却很脆弱。ASE 的研究显示,旧载板的抗冲击韧性较新载板显著下降,边缘出现了约 43 微米的崩边和微缺陷。这并不意味着载板不能复用,而是提醒业界:如果缺乏量化的边缘完整性检测,重复利用载板无异于一场豪赌。 随着面板尺寸变大、载板成本攀升,这一监管真空必须被填补。

面板尺度的翘曲博弈

在面板级封装中,翘曲(Warpage)常被误认为只是末端的封装质量问题,因为它直观地表现为成品的弓起或卷曲。但问题的根源远比这早得多:它始于所选材料的固有属性,始于聚合物在固化与热循环中的物理响应,始于铜密度梯度对堆栈刚度平衡的破坏,更始于每一步工序留下的残余应力在进入下一环节前的不断叠加。在晶圆尺度下,几何形状的对称性与成熟的工艺经验尚能压制这种累积;但在面板尺度下,同样的物理力作用于更大的面积,却缺乏足够的结构支撑。如果不用专用材料从头构建,管理的容错空间将极其狭窄。

临时键合层(Temporary Bonding Layer)是面板工艺中被严重低估的翘曲变量。 在晶圆级加工中,键合材料已历经数年的生产验证,其行为模式在标准工艺下是高度可预测的。然而,当同样的材料被要求在大面积面板上实现均匀涂覆、在更重的机械负荷下保持厚度一致,并经受比原设计更严苛的热冲击时,挑战便接踵而至。

Brewer Science 的封装方案工程师 Hamed Gholami Derami 指出:“临时键合材料的总厚度偏差(TTV)直接决定了减薄器件的质量与均匀性。为了满足 HBM DRAM 等芯片所需的极限减薄要求,必须开发具有更高热稳定性和机械稳定性的新型临时键合材料。”

键合层偏差的后果具有“前向传播性”,且事后几乎无法修正。 如果键合层在 310mm 面板上的涂覆不均,随后的研磨工序就会产生厚度参差不齐的器件。这种偏差会进一步拖累后续的对准精度,破坏互连良率,最终反噬那份让面板格式起初看起来极具吸引力的“经济账”。

挑战并未止于面板本体。在玻璃面板上构建再布线层(RDL),对材料的要求已逼近当前基板级光刻技术的极限。面对目前面板级 RDL 追求的线宽/线距(L/S)分辨率,标准的光刻胶和配套化学品正面临“余量枯竭”。此外,在大尺寸面板上实现超高叠层对准精度(Overlay Accuracy),其难度也远超传统有机基板行业的日常经验。

Fraunhofer IZM 组长 Lars Boettcher 强调:“针对 2 微米甚至更细的分辨率,迫切需要探索新型光刻胶。同时还需考虑配套的新型设备,例如用于涂覆后固化的大型热板。”

目前,能够处理大型矩形格式的面板级 CVD(化学气相沉积)和 PVD(物理气相沉积)工具才刚刚露头。大尺寸液态介质材料的涂覆与开发设备尚未标准化。更不用说,处理面板级流程产生的海量计量与工艺控制数据,本身就是一项重大的工程挑战。这些问题虽然并非无解,但在面板级封装的经济蓝图变现之前,每一个堡垒都必须被攻克。

键合界面的良率挑战——规模化的代价

在面板级 Chiplet(芯粒)集成中,混合键合(Hybrid Bonding)的引入让原本就棘手的基板问题雪上加霜。混合键合能提供传统凸点(Bump)连接无法企及的互连密度;对于追求低功耗、高带宽、异构集成的 AI 加速器而言,这种密度优势正变得不可或缺。然而,混合键合极其“眼里容不得沙子”,它对误差的零容忍,恰好与面板加工引入的各种不确定性形成了剧烈冲突。

混合键合发源于前道晶圆厂(Foundry),在那里,“洁净度”是工厂设计的核心参数。 从空气循环系统到设备表面,再到工艺化学品的纯度,一切都为了杜绝任何可能摧毁良率的颗粒污染。然而,处于后道的封测厂(OSAT)在设计之初并未考虑如此苛刻的环境假设。随着混合键合向后道迁移以支持基于面板的芯粒封装,工艺的高标准与环境的现状之间出现了巨大裂痕,必须通过其他手段来弥补。

Amkor 副总裁 Mike Kelly 指出:“随着混合键合从晶圆厂下沉到封测厂,处理颗粒污染成了头等大事。 哪怕是一个纳米级的颗粒,也足以让玻璃基板局部‘翘起’,从而毁掉版面上的大量单元。在晶圆厂,你身处超洁净环境;但在封测厂,微小颗粒就是良率的‘丧钟’。”

为了应对这一局面,设备供应商正在开发集群化工具(Cluster Tools)。这种设备通过在机器内部维持局部的“微环境洁净度”,试图在不要求整个工厂升级的前提下,达到晶圆厂级别的洁净标准。这虽是一个可行的工程方案,却显著增加了成本与系统复杂度。而且,在多大的面板、什么样的生产条件下,多高的局部洁净度才算“达标”?目前尚缺乏足够的生产数据来给出定论。

在面板尺度下,一旦失误,代价将呈几何倍数增长。同规模的污染事件发生在超大面板上,受灾的单元数量远多于圆形晶圆。良率损失带来的经济冲击,将随着版面面积的扩大而同步放大。

模拟未竟之境——为“不存在”的结构设计工艺

为尚未实现大规模量产的结构设计工艺流程,本质上是一场“摸着石头过河”的挑战。玻璃在大尺寸面板尺度、真实工艺环境下的物理行为,目前尚未得到完整的表征。 工程师所依赖的仿真工具,其验证基础是晶圆级的几何形状与工艺流;而那种经过数十年晶圆制造打磨、在“模型预测”与“产出结果”之间形成的精准闭环反馈,在面板级领域才刚刚起步。

面板级加工所承载的设计复杂度,让这一挑战变得愈发具体。 衡量先进封装组件尺寸的一个实用指标是“光刻掩模场(Reticle)”。顶尖光刻设备的单次曝光面积约为 26mm x 33mm。超过此面积的封装需要将多次曝光“缝合”在一起,因此,一个设计跨越的掩模场数量,已成为衡量其规模与复杂度的行业简语。

Synopsys 研发执行总监 Sutirtha Kabir 表示:“设计规模正从几个掩模场激增到更多。业内正在讨论,到本个十年末,封装尺寸将向几十个掩模场迈进。目前有机中介层中已经嵌入了数十个硅桥,设计极其复杂,EDA(电子设计自动化)在其中扮演着至关重要的角色。”

将这一趋势具象化:一个跨越 42 个掩模场的设计,其尺寸约为 100mm x 150mm 甚至更大。 这已深深刻入面板级的版图,远超晶圆级加工的经济承载力。Kabir 提到的 30 多个嵌入式硅桥绝非细枝末节,每一个都是需要精密对准的组件;而构建这种复杂结构所引入的累积应力,正是目前的仿真工具在面板尺度上仍处于“学习阶段”的多变量难题。

模拟一个包含 30 多个嵌入式硅桥的结构,在经历 20 步面板级工艺序列(每一步都引入新应力并承接前序“前科”)时的动态行为,其计算逻辑与模拟 300mm 晶圆有本质区别。仿真库中的标称材料属性仅能作为起点,特定玻璃配方在特定固化与热序列下的实际表现,与理论值的偏差只有通过生产实践才能揭晓。 然而,制造商往往不愿共享这些能让模型更精准的工艺数据,因为那代表着他们历经艰辛才获得的竞争壁垒。

结语:前路之形

随着面板级封装从研究阶段迈入活跃的工程化阶段,一个事实愈发清晰:其核心挑战并非传统意义上的封装问题,而是恰好在封装语境下被解决的“材料与工艺集成”挑战。

玻璃面板能否实现高可靠性的量产,取决于表面处理、金属化、热循环行为以及临时键合材料的表现。封测厂能否在间距持续缩减的情况下维持混合键合良率,取决于污染控制、CMP(化学机械抛光)管理以及铜在细间距下的机械极限。

这些问题无一能被孤立解决。那些转型最成功的公司,正将此视为一个“以封装为集成层”的材料与工艺集成问题,而非单纯将材料视为辅助条件的封装问题。

驱动“第二波浪潮”的经济动力是真实的,且随着 AI 封装尺寸的膨胀,这种动力只会增强。面向造价更高、面积更大的封装,面板级加工的成本优势将愈发凸显。然而,从“诱人的经济账”到“可靠的生产线”,其间横跨着极具挑战的硬核工程问题。 前行的节奏,取决于在一个尚未大规模成形的制造环境中,行业积累生产经验的速度。

- 收藏