ASML:人工智能时代的光刻创新

摘要

人工智能(AI)应用正加速半导体产业增长,同时催生光刻设备新需求。其技术根基在于工艺创新:包括新架构晶体管设计、基于晶圆级键合(wafer-to-wafer bonding)的新型集成方案,以及尖端封装技术。本文系统阐述支撑AI技术迭代的深紫外光刻(DUV)设备关键技术演进路径。

1.引言

六十载光阴流转,戈登·摩尔1965年论文中的核心预言仍熠熠生辉:

- 微缩化与成本定律:集成电路持续微缩与元件成本下降,不断驱动电子产品普及("proliferation of electronics")及其在新领域的渗透

- 系统集成经济学:特定场景下,"以独立封装互连的小型功能单元构建大型系统"被验证更具经济性,整体单位成本与良率成为技术路线的关键决策因素

- 成本引力永恒:降低成本始终是"集成电路技术的核心吸引力"

人工智能(AI)已迅猛成长为半导体产业的核心增长引擎,正加速实现摩尔预言的电子化浪潮。本文系统阐释:

- AI技术如何重塑终端市场格局

- 支撑"小型功能单元集成"的器件与工艺技术突破

- ASML深紫外光刻(DUV)技术路线如何协同极紫外光刻(EUV)演进,构建面向AI时代的光刻解决方案矩阵

2.终端市场:多元增长引擎

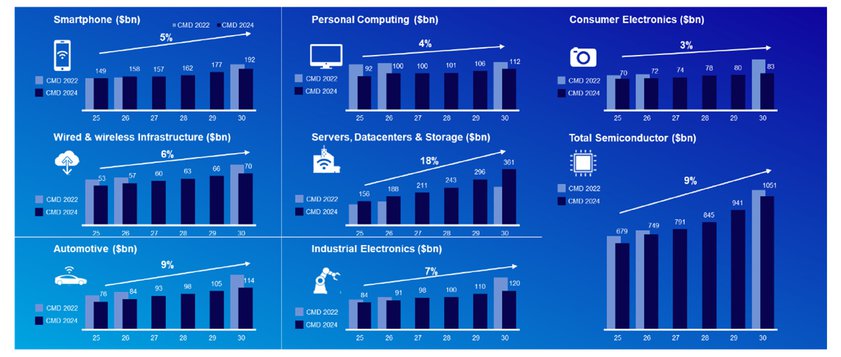

技术革新加速催化的社会变革持续拓展半导体应用疆域,全球半导体市场规模预计2030年突破万亿美元大关。

图1:多重社会宏观趋势正驱动半导体创新与市场增长(来源:ASML)

叠加此趋势,人工智能的迅猛突破正注入新增量动能,其中服务器、数据中心及存储领域成为核心增长极。

图2:半导体销售额预计以9%年复合增长率攀升,2030年突破万亿美元(来源:ASML)

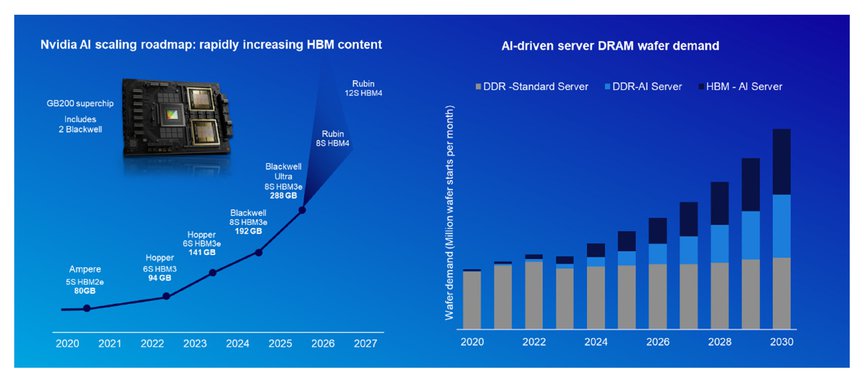

AI GPU/CPU技术路线的快速迭代,与内存存储及数据传输能力的创新突破形成战略协同。

图3:至2030年AI服务器DRAM月产能需求或达百万片晶圆(来源:Nvidia Investors 2024 年 10 月投资者报告、ASML)

3.器件与工艺技术突破

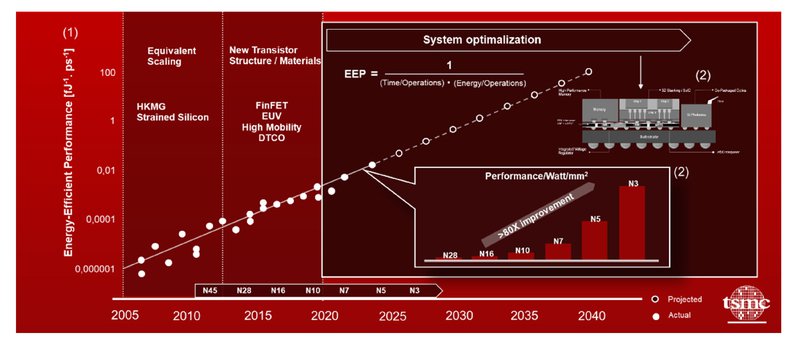

半导体制造商持续探索创新路径,在提升单位面积功能密度的同时,应对能效比的核心挑战——无论移动设备抑或高性能计算领域,能耗优化需求已成关键制胜要素。

图4:逻辑器件技术路线延续性(展望至2030年代末)(来源:IMEC,ASML)

图5:未来二十年摩尔定律演进路线

(来源:台积电刘德音《Unleashing the future of innovation》ISSCC 2021.2.15;刘德音、黄汉森《IEEE Spectrum》2024.3.28;Kevin Zhang《Semiconductor Industry: Present and Future》IEEE固态电路会议2024.2;Martin van den Brink ITF 2024)

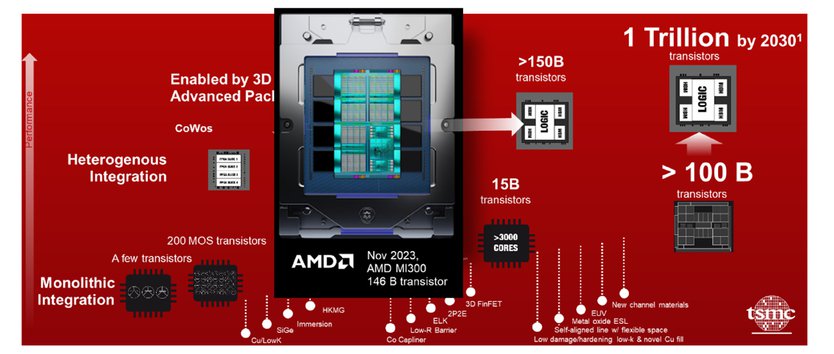

正如摩尔所言,构建大型计算系统的经济路径在于将其解构为小型功能单元,并通过封装技术实现系统集成。

图6:2023年迈向万亿晶体管量级集成器件

(来源:Kevin Zhang台积电《Semiconductor Industry: Present and Future》IEEE固态电路会议2024.2;刘德音、黄汉森《IEEE Spectrum》2024.3.28;Martin van den Brink ITF 2024)

(来源:Kevin Zhang台积电《Semiconductor Industry: Present and Future》IEEE固态电路会议2024.2;刘德音、黄汉森《IEEE Spectrum》2024.3.28;Martin van den Brink ITF 2024)

先进封装技术创新与晶体管技术突破协同推进,预计2030年前将实现单颗(异构)集成器件承载万亿晶体管目标。

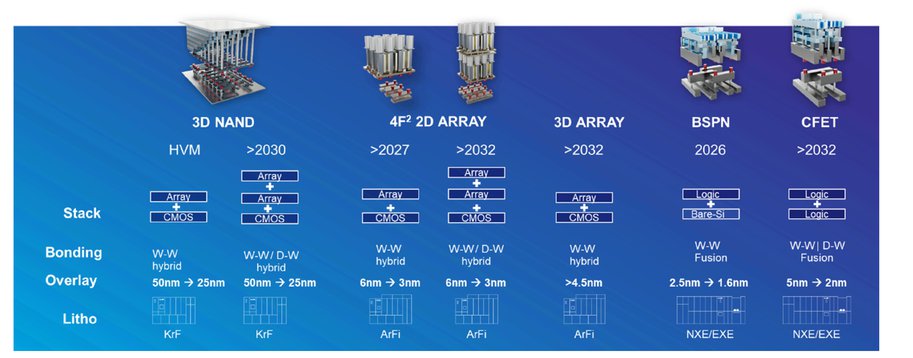

本文聚焦的封装创新技术主要包括两类:

- 水平互连技术:通过图形化中介层(Redistribution Layer, RDL)构建平面互连网络

- 垂直互连技术:采用硅通孔(Through Silicon Via, TSV)实现三维堆叠互连

- 前端晶圆键合(Front end wafer-to-wafer bonding)作为关键使能技术,赋能"解构-集成"范式,实现复杂系统的功能模块化构建。

图7:晶圆键合工艺体系与应用场景(来源:ASML)

4. DUV光刻产品技术矩阵

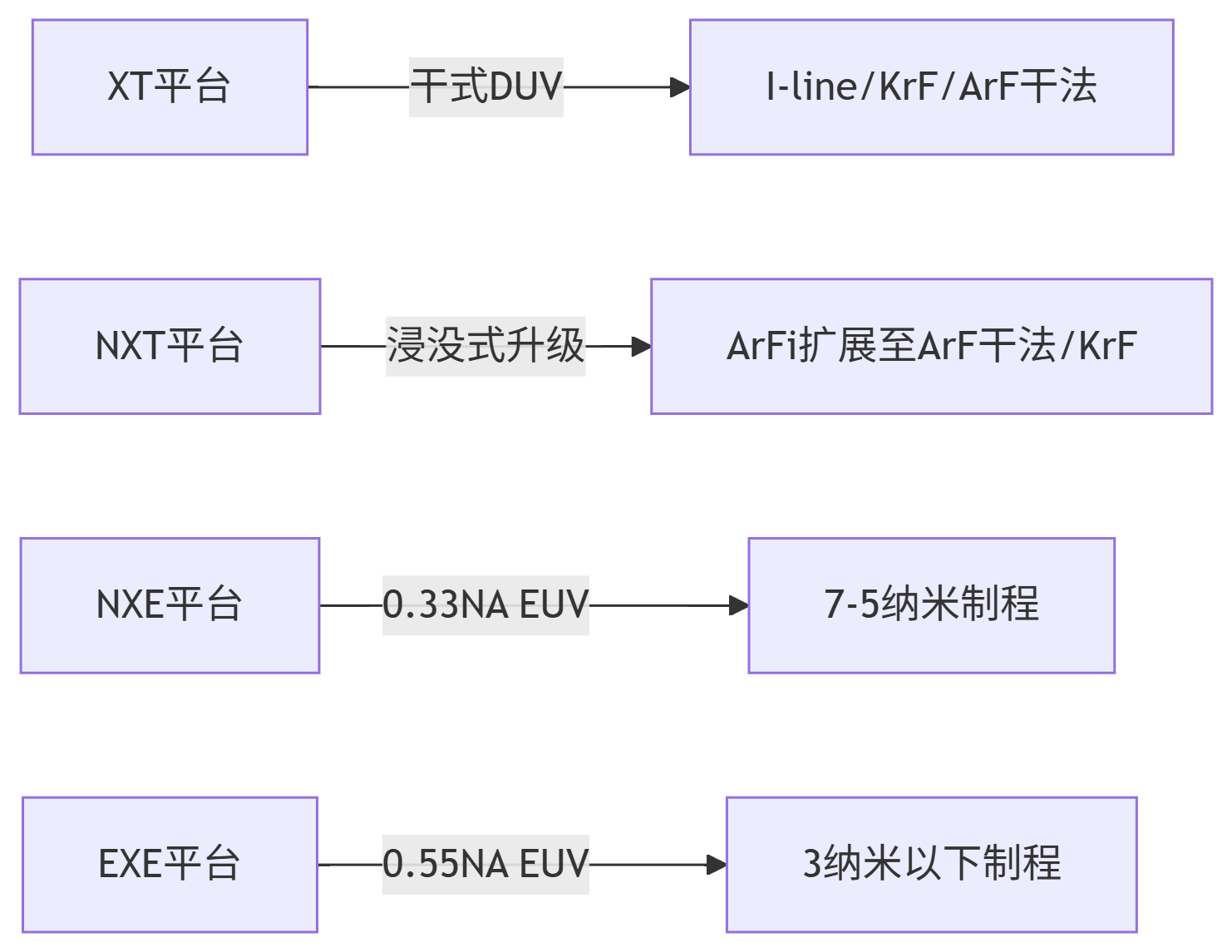

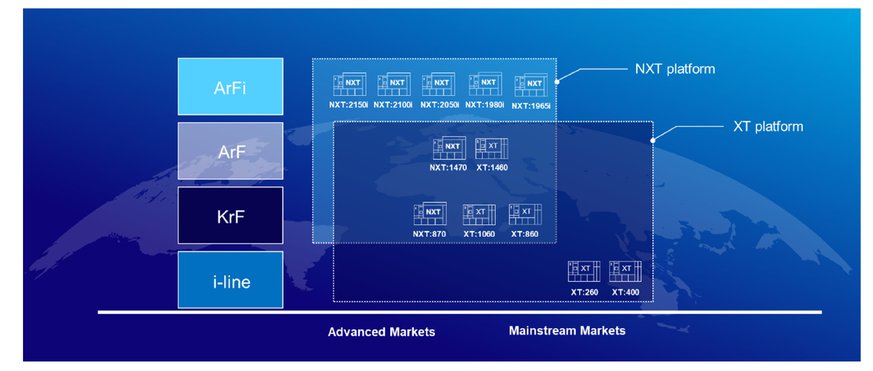

ASML光刻设备技术谱系覆盖365纳米(I-line)至13.5纳米(EUV)全波长解决方案,具体包括:

该技术体系通过四大光刻平台协同支撑:

图8:ASML DUV光刻产品技术矩阵

我们凭借广泛的产品矩阵,通过跨平台创新资源调配与技术协同效应,为客户技术路线提供成本最优解决方案。

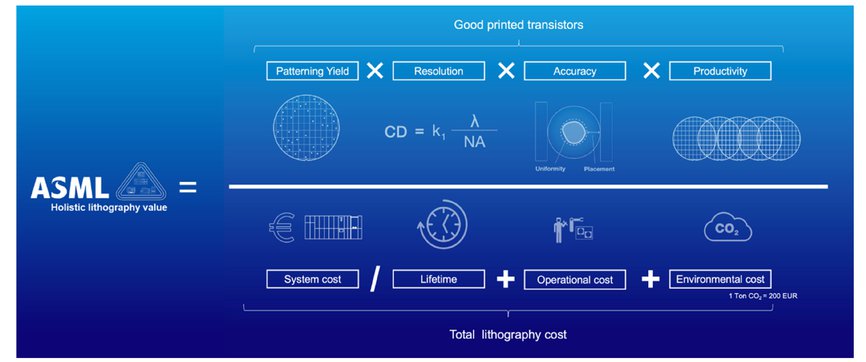

总结与人工智能相关的关键市场和客户需求,我们的当务之急包括不断降低客户成本以支持他们的技术路线图,同时开发支持几何缩放和先进封装路线图的创新解决方案,以及支持二维和三维集成的过程控制技术。

我们降低成本的主要目标是尽量减少工艺步骤,这主要通过降低边缘定位误差 (EPE),即在更高的精度下提高成像分辨率来实现。我们目前的 EUV 产品组合主要致力于实现这一目标。

图9:ASML全域创新战略与市场需求对应关系

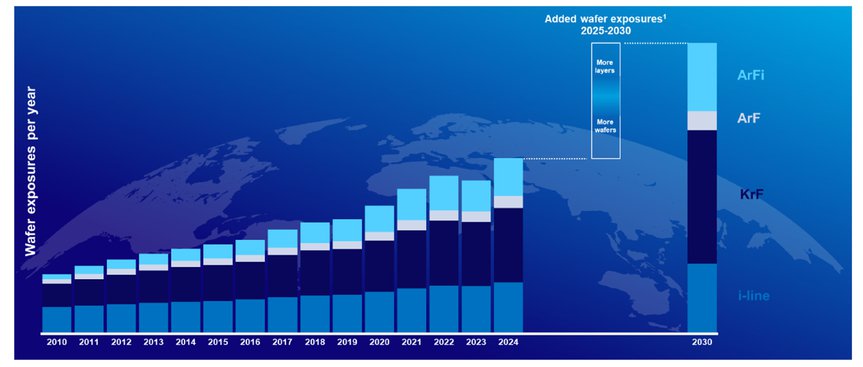

另一个推动客户价值的重要杠杆是生产力。为了提升产能,我们专注于KrF:这项技术支持最多数量的晶圆曝光,并且由于28纳米及以上工艺节点逻辑制造的增长,以及3D NAND中KrF层数的增加,它已成为增长最快的细分市场之一。

图10:年度晶圆曝光量波长分布(仅DUV)(来源:ASML)

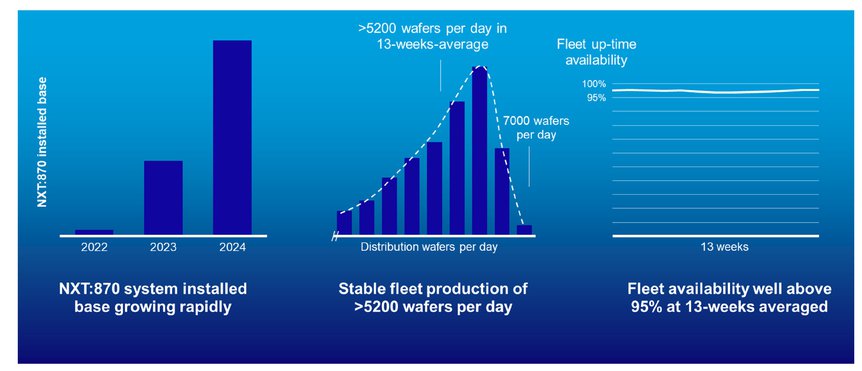

基于该波长的广泛应用,我们将其定位为产能规模提升的核心载体:第一步技术举措为引入NXT平台旗舰机型NXT:870,并于2022年启动设备交付。

NXT:870装机量正快速增长,凭借340片/时(WpH)的通量产能,已创下日均产能突破7,000片晶圆(WpD)的行业纪录。

图11:NXT:870设备广泛应用及其产能快速增长态势(来源:ASML)

NXT:870B机型已于2024年末季度启动交付,作为第二代NXT KrF光刻设备,成为业界首款实现400片/时(WpH)通量产能的光刻系统。

图12:ASML最新款KrF光刻设备NXT:870B

NXT:870B的核心创新在于工作台技术领域,本设备成功移植了浸没式ArF光刻(ArFi)及高数值孔径EUV(EXE平台)的技术突破。

除实现业界最高产能外,将NXT技术引入KrF平台还显著提升了套刻精度。NXT:870卓越的套刻能力源于工作台系统与光学透镜设计的协同创新——其工作台技术源自ArFi NXT平台,而掩模台技术则继承自高数值孔径EUV系统。

新型透镜的校正能力可优化产品套刻精度,同时得益于浸没式技术的突破性进展,系统能在保持通量产能的前提下,实现对晶圆上更多对准标记的精准定位。

NXT:870B系统搭载的增强型焦深技术成为关键创新,为光学图像传感器及闪存器件提供超分辨成像能力。该技术通过多焦成像系统(Multifocal Imaging)实现:

- 厚胶工艺中特征结构的精准成像

- 成像步骤缩减达40%

- 显著降低生产成本

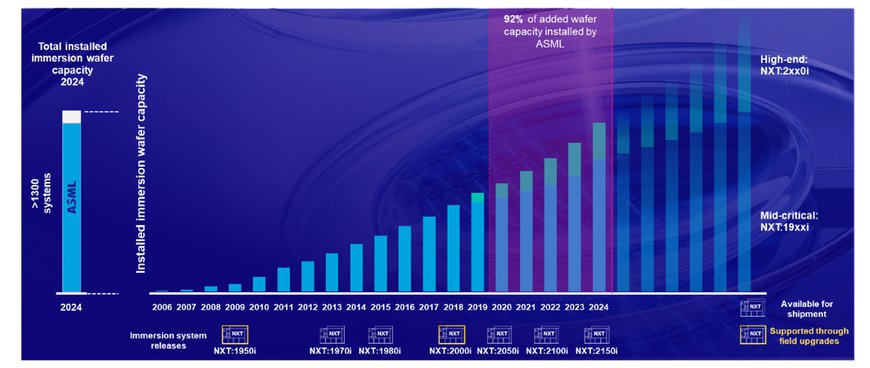

在浸没式ArF光刻领域,我们持续交付全系列机型。鉴于每代设备针对特定制程节点优化设计,客户可精准匹配设备类型与工艺层需求,实现资本支出(CapEx)最优化。

图13:ArFi设备装机产能与现役产品矩阵

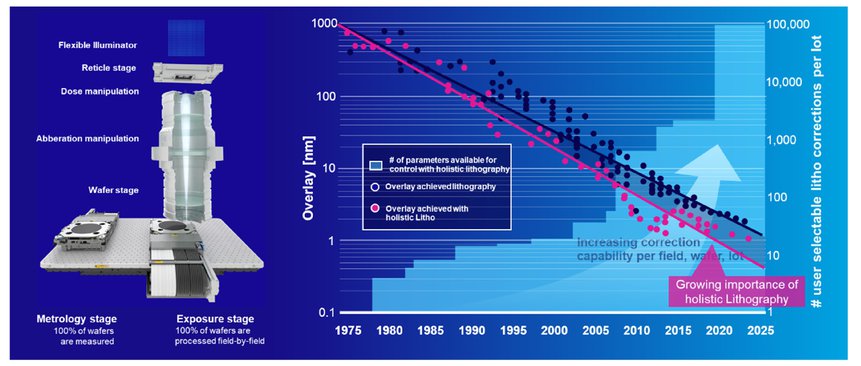

高端光刻系统通过精密传感器阵列(在线/离线双模监测)实现独特工艺校正功能,可在曝光场内、晶圆间实施海量参数校正。

图14:光刻系统工艺校正能力示意图

折反射光学系统突破

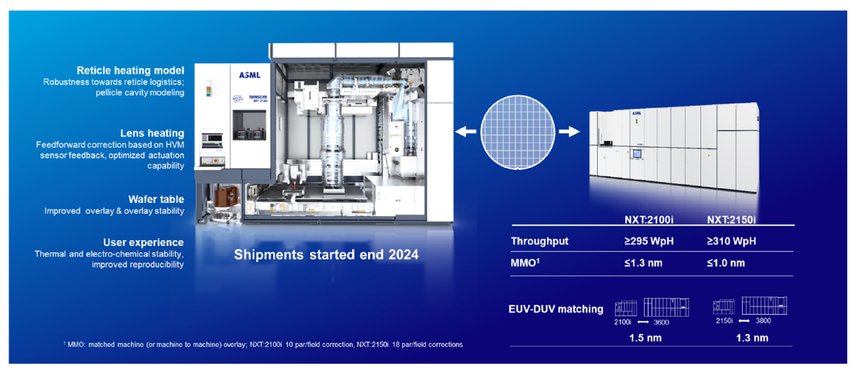

采用折反射复合镜头设计²(融合折射与反射光学元件),ArFi技术实现极致校正能力³。最新旗舰机型NXT:2150i在提升产能的同时,达成深紫外光刻领域顶尖套刻精度。

图15:NXT:2150i核心特性与关键技术指标综述

光刻系统智能校正演进

光刻机建模与控制界面的技术突破,结合透镜校正元件的灵活性升级,赋能系统实施更精密的制程补偿:

- 客户应用场景补偿:精准抵消制程波动与客户应用效应

- 扫描方向场内校正:实现曝光场内扫描轴向的实时补偿

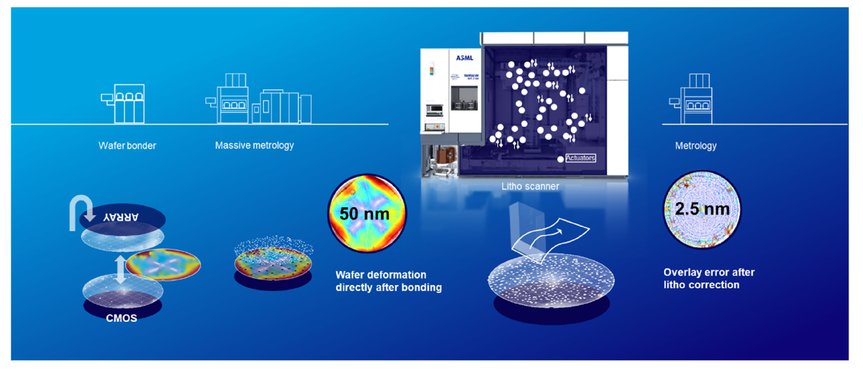

晶圆键合技术支撑

随着晶圆键合技术在不同应用场景中的拓展,其引发的局部/全局晶圆形变问题凸显。光刻系统校正能力成为客户导入该技术⁴的关键使能要素。

图16:海量量测技术与光刻校正能力协同实现键合后套刻补偿

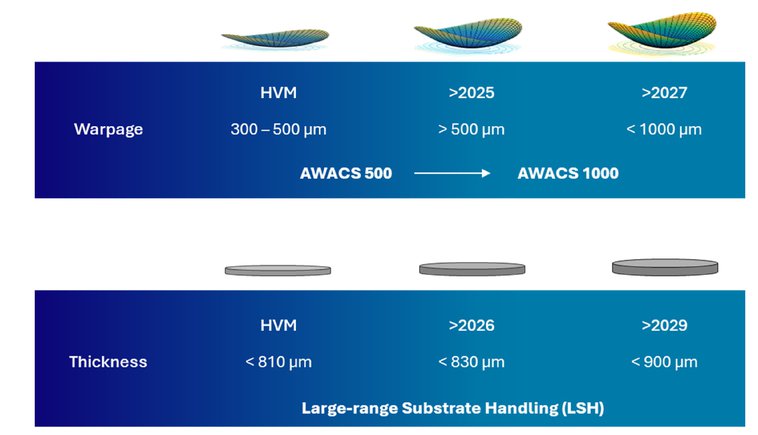

光刻技术应对3D器件演进

随着客户制程技术迭代,光刻系统需具备处理高厚度晶圆(≤900μm)与强物理形变(翘曲≤1000μm)的关键能力。为支撑未来技术节点发展(尤其是3D NAND等垂直堆叠存储技术),光刻设备亟需突破性创新。

晶圆形变控制技术突破

浸没式与干式光刻系统通过先进晶圆夹持系统(AWACS)实现:

- 超限形变处理:可应对高达1000微米的复合物理形变

- 极厚晶圆兼容:900μm厚度晶圆制程能力(当前研发中)

图17:3D器件技术路线与ASML厚晶圆/高形变晶圆处理创新方案

全领域应用与封装突破

I-line光刻设备覆盖全产业链场景,其新兴应用聚焦先进封装领域。

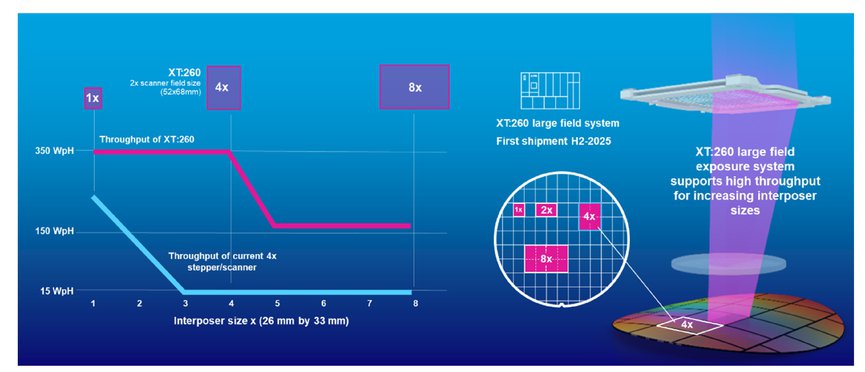

革命性新品发布

ASML最新I-line光刻设备XT:260将于今年启动交付——作为业界首款大视场光刻系统¹⁶,专为多掩模封装中介层(multi-reticle packaging interposer)应用提供业界最高产能效能。

图18:ASML下一代I-line光刻设备XT:260¹⁶

图19 XT:260光刻系统将赋能多掩模封装应用实现业界最高产能

该设备配备0.35数值孔径透镜,具备:

- 超大曝光视场:52×68毫米(标准设备2.3倍)

- 成像分辨率:400纳米(满足先进封装线宽要求)

- 通量产能:350片/时(WpH)

利用 XT:260,我们为先进封装和前端应用提供经济高效的解决方案,包括处理多掩模版基板的能力、处理厚晶圆和翘曲晶圆的能力以及对准能力。

5.结论

六十年过去了,戈登·摩尔的预测依然正确;硅器件和应用的蓬勃发展仍在继续,计算方式的创新也在半导体器件和工艺的进步推动下持续推进。成本仍然是技术替代方案之间的制约因素,也是加速增长的最重要杠杆。

ASML 独特的产品组合能够不断推动多轴创新,通过简化流程和降低每次曝光成本来优化客户成本,为越来越多的设备基板提供处理和控制能力,同时实现新颖的设计和制造方法来服务于不断发展的行业。

Notes

[1] “Cramming more components onto Integrated Circuits”, Moore, G.E., Electronics 38 (1965)

[2] Bernard Kneer et al., “Catadioptric lens design: the breakthrough to Hyper-NA optics”, Proc. of SPIE Vol. 6154 615420-3

[3] Michiel Kupers; Dongsub Choi; Boris Habets; Geert Simons; Erik Wallerbos, “Non-linear methods for overlay control”, SPIE 6518, Metrology, Inspection, and Process Control for Microlithography XXI, San Jose, Feb, 2007

[4] Richard van Haren, at all, ASML, EVG, Leti:, “Characterization and mitigation of local wafer deformations introduced by direct wafer-to-wafer bonding“, SPIE Advanced Lithography + Patterning, 2024

原文

Alberto Pirati, Jeannot Driedonkx, Wim de Boeij, Elliott McNamara, Jeroen de Groot, Jorgen Kool, Peter ten Berge, Michael Kubis, Daan Slotboom, Gianluca Gattobigio, Aditya Deshpande, Jean Philippe van Damme, Antoine Kempen, Ahmed Zayed, Mohamed el Kodadi, Stefan Keij, Arjan Gijsbertsen, Yzzer Roman Gutierrez, and Saurabh Singh "Lithography innovations for the artificial intelligence era", Proc. SPIE 13424, Optical and EUV Nanolithography XXXVIII, 134240H (22 April 2025); https://doi.org/10.1117/12.3050947

说明:本文仅作为学习分享,如有侵权请联系我们删除

- 收藏