纳米压印技术的挑战与展望

近年来,半导体器件遵循摩尔定律持续微缩化并取得显著进展。尤其在DRAM(动态随机存取存储器)领域,极紫外光刻技术(EUV)的引入有力推动了微缩化进程。然而,EUV光刻的技术瓶颈正逐渐显现,纳米压印光刻(NIL)作为新一代微缩化技术备受瞩目。本文基于报告内容,系统阐述NIL技术在DRAM制造领域的现状与挑战,剖析其未来发展前景,并探讨该技术实用化进程中的核心问题,进而展望半导体微缩化技术的演进方向。

2.引言

半导体产业的微缩化技术,尤其在DRAM领域持续迭代演进。2020年,三星电子率先在DRAM行业引入极紫外光刻(EUV)技术,其后SK海力士与美光科技亦加速推进EUV技术落地。尽管相较于传统氩氟浸没式光刻(ArF immersion lithography),EUV技术能实现更精细的图形化制程,但其成本攀升与工艺控制复杂性等挑战也随之凸显。

以美光科技的技术路线为例:其在1B系列制程中引入先进CMOS技术,并于1γ世代将EUV光刻应用于布线工艺,积极推进面向微缩化的技术创新。然而在1ε世代之后的DRAM微缩化进程中,不仅需要突破新的技术瓶颈,平面型DRAM的物理极限也逐渐显现。在此背景下,纳米压印光刻(NIL)技术凭借其替代或补充EUV光刻的潜力,正引发业界高度关注。

3.主要论述

本次报告重点探讨了纳米压印技术(NIL)替代极紫外光刻(EUV)的潜力及其产业化应用面临的具体挑战。

3-1 NIL技术优势与发展潜力

在阐述EUV光刻现状与挑战的基础上,报告聚焦NIL技术突破点:以SPIE 2024会议展示的切割制程应用为例,着重指出叉指状纳米压印图形具有特殊构型优势——即便采用EUV光刻亦难以实现。此案例表明,NIL技术不仅具备微缩化潜力,更在复杂结构成形方面超越EUV技术局限。该技术有望通过简化工艺流程、优化厂房空间利用率,最终实现整体产能提升,同时展现出显著的成本控制优势。

3-2 NIL技术应用挑战

然而报告同时指出,NIL技术产业化仍存在多项技术瓶颈亟待攻克:

3-3 对准标记尺寸瓶颈

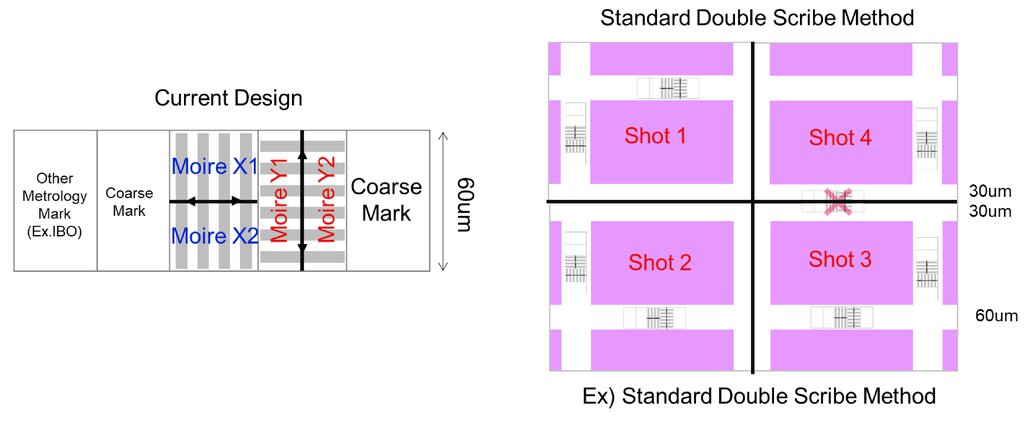

如图1所示,当前NIL设备需依赖TMM标记(高阶修正对准标记)实现压印对准,但器件制造商要求缩减切割道尺寸并相应缩小标记面积。现有TMM标记规格无法满足该需求,亟需开发微型化对准标记。对策建议包括:引入基于莫尔条纹标记的对准分析系统,并通过优化设计降低标记边缘眩光效应影响。

图1 对准设计问题

3-4 压印间隙瓶颈

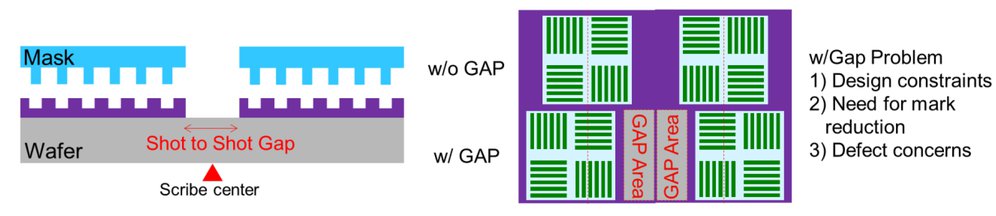

压印间隙的存在不仅阻碍喷墨式光阻涂布工艺的实施,更限制切割道中心区域的有效标记布设空间,同时引发制程中颗粒污染的显著隐患。当前行业正致力于将现有4微米间隙向零间隙过渡,但由此衍生出胶体溢流(抗蚀剂覆盖相邻压印标记)等新型技术挑战。解决此难题的核心突破口在于提升NIL设备工作台精度与模板定位精度。

图2 压印单元间隙技术问题

3-5 表面粗糙度瓶颈

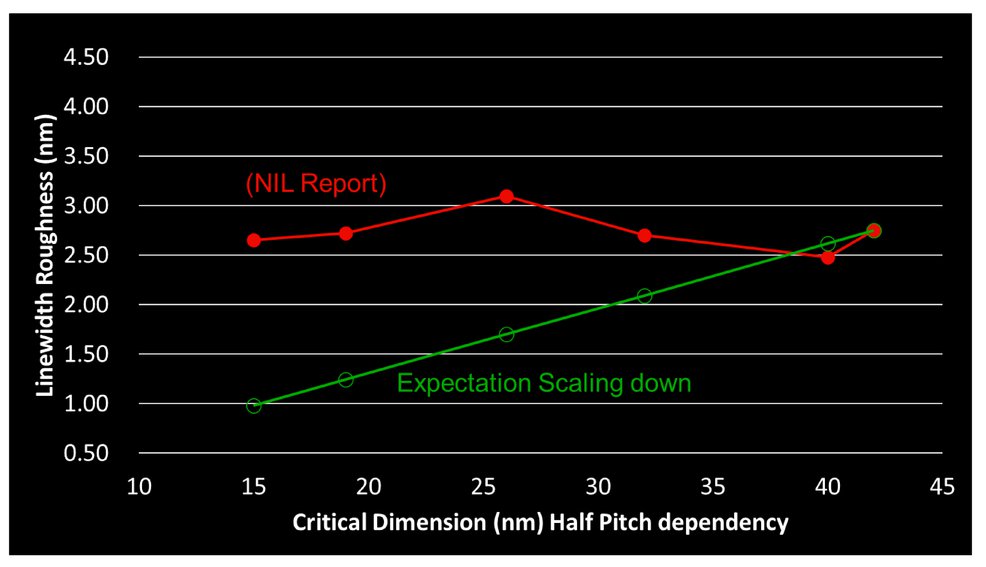

现行掩模工艺对表面粗糙度的改善尚不充分。随着微缩化进程推进,粗糙度问题须以图形节距比(pattern pitch ratio)为基准进行量化评估,且亟待制定更严苛的粗糙度控制目标。当前应对策略包括:掩模材料从传统铬基转向三层复合掩模(Tri-layer mask)或碳基掩模;针对电子束光刻(EB lithography)抗蚀剂,需协同优化低感光度与粗糙度改善的平衡关系。

图3 表面粗糙度演进趋势瓶颈

3-6 模板寿命与成本瓶颈

模板寿命及成本是NIL技术产业化的关键制约因素。其中,降低重复性缺陷(repeater defects)可直接延伸模板使用寿命并控制成本,这需要采取多维度改进策略:优化脱模工艺(release process)、调控掩模表面能(mask surface energy)、革新预处理技术,并开发可在紫外曝光后修饰表面的新型抗蚀剂。

3-7 缺陷控制瓶颈

降低重复性缺陷是NIL技术核心挑战。该缺陷在存储器器件中尚可修复,但对逻辑器件具有致命影响。理想目标需将重复性缺陷归零,这要求实施涵盖抗蚀剂颗粒管控、设备颗粒清除及预处理优化的系统性解决方案。

3-8 技术挑战综述

对准标记挑战

扩大标记尺寸将加剧切割道占用率(见图2),故非可行方案。通过优化标记设计与光学系统,可实现TTM标记的微型化突破。

压印间隙挑战

压印间隙不仅制约标记设计自由度,更可能导致套刻精度劣化。切割道间狭缝结构还存在制程缺陷隐患。提升压印定位精度与掩模模板制造公差,是缩小间隙的关键路径。

表面粗糙度挑战

本报告指出掩模模板的电子束曝光(EB)是主要诱因。突破方向需重构现有工艺:抗蚀剂改良虽重要却不足够,必须引入三层复合掩模或碳基硬掩模;针对20nm以下图形,建议采用基于侧壁工艺的自对准双重成像技术(SADP)。

缺陷控制挑战

缺陷问题是纳米压印最大技术短板。理想状态下重复性缺陷必须达成零容忍目标,该突破亦将延伸掩模寿命。技术突破点包括:

- 模板表面材料改性

- 喷墨抗蚀剂颗粒剔除技术

- 脱模性能强化方案

- 表面亲水化处理工艺

结论

本报告论证了纳米压印技术(NIL)在DRAM制造领域替代极紫外光刻(EUV)的创新潜力——尤其在平面型DRAM微缩化逼近物理极限的背景下。NIL技术具备成形特殊结构的独特能力(其构型复杂度超越EUV光刻极限),成为该技术的核心竞争优势。与此同时,产业化进程中的五大技术壁垒亦得以明确:对准标记精度、压印间隙控制、表面粗糙度优化、模板寿命成本及缺陷归零目标。

报告强调:唯有通过全行业协同攻坚,实现技术瓶颈透明化共享,方能推动NIL技术生态的整体进化。挑战共担与前景共绘,将成为孕育下一代半导体设备与技术突破的基石。综上,尽管NIL产业化道阻且长,但预计2026节点前将涌现突破现有壁垒的NIL量产设备,亟需产业链全方位赋能。本文基于纳米压印技术研究体系,系统剖析发展现状、核心挑战及未来路线,明确指出:产学研政深度协同与全行业技术共进,是NIL技术开辟半导体微缩化新纪元的必由之路。

原文

Tomohiro Iwaki, Kiyohito Yamamoto, Masayuki Kagawa, Hideki Cho, Takaharu Nagai, and Hisayoshi Watanabe "Nanoimprint technology issue and outlook", Proc. SPIE 13427, Novel Patterning Technologies 2025, 1342707 (24 April 2025); https://doi.org/10.1117/12.3051901

说明:本文仅作为学习分享,如有侵权请联系我们删除

- 收藏