硅光子技术与共封装光学(CPO)面临的测试瓶颈

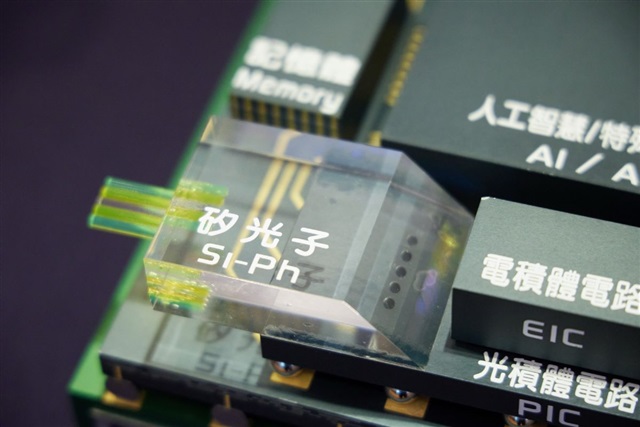

AI 需求正将数据传输推向极限,使得 2026 年成为硅光子(SiPh)与共封装光学(CPO)迈向大规模部署的关键一年。整个半导体行业都在加速研发,力求将这些技术商业化。

目前的压力已转移到供应链中一个隐秘但至关重要的环节:测试。

根据封测端(backend)消息人士透露,硅光子测试分为三个阶段。主要的瓶颈在于第二阶段——“Insertion 2”,该阶段负责晶圆级电光集成测试,仍是测试流程中最困难的一步。

核心挑战:Insertion 2 “黑洞”

其挑战在于需要在多变的环境下,同时测试电信号和光信号。目前尚未有成熟的自动化方案能应对大规模量产,这使得 Insertion 2 成为限制硅光子规模化生产的关键障碍。

在先进封装领域,这一问题尤为突出。基于TSMC(台积电)SoIC 封装的芯片将电子和光子芯片堆叠成紧凑的光学引擎,这些引擎必须经过双面晶圆测试才能筛除缺陷。

业内人士将 Insertion 2 描述为“黑洞”:其吞吐量低测试效率极慢;并且测量准确性难以保障,精度难维持;同时成本高昂,为 ATE(自动测试设备)供应商和接口供应商开发兼具可扩展性与成本效益的自动化方案已成为核心挑战。

供应链的应对与现状

在客户交付时间的压力下,包括 Advantest(爱德万测试)、Teradyne(泰瑞达) 等测试设备商,以及 FormFactor、MPI Corporation(旺矽科技) 和 Hermes Testing Solutions(先睿检测) 等接口供应商,都在加速开发晶圆级电光测试方案。

相比之下,其他阶段已较为成熟:比如Insertion 1针对光子集成电路(PIC)测试,已有自动化方案。针对 CPO 封装后的成品测试的Insertion 3,方案也已到位。

Advantest 表示,其与 FormFactor 合作开发的 “Triton” 系统正在进行客户端调试,预计将于年底部署用于光子 IC 测试。对于Insertion 2阶段相关方案预计在上半年完成概念验证(PoC),下半年有望开启客户共同开发。

未来趋势:左移测试(Shift-Left Testing)

随着硅光子技术迈向高速部署,对稳定性和准确性的要求不断提高,测试门槛随之抬升。由于 CPO 封装后的失效成本极高,业界正迫切需求早期验证,从而推动了“左移测试”(即在生产流程更早期进行测试)的趋势。

如果 Insertion 2 的瓶颈持续存在,测试厂在生产初期可能会选择跳过该阶段,直接依赖 Insertion 3(终测)。但这将是一种无奈的折衷:以较低的良率和较高的生产成本为代价,换取按时出货。

- 收藏