玻璃基板发展势头强劲

封装尺寸越大,优势越显,但诸多难题尚待攻克。

作为封装基板,玻璃的优势是巨大的。它极其平整,且热膨胀系数低于有机基板,这简化了光刻工艺。

而这仅仅是个开始。对于多芯片封装而言日益严重的翘曲问题,玻璃能极大地减少这一问题。芯片可以通过混合键合连接到玻璃上的再分布层(RDL)焊盘。并且,相对于有机芯基板,玻璃为高频和高速器件提供了极低的传输损耗。

如果这还不够,硅中介层和有机芯基板正逐渐力不从心。玻璃比硅中介层便宜得多,并且翘曲减少50%,位置精度提高35%。这使得制造线宽/线距小于2µm的再分布层(RDL)变得更容易,而有机芯基板难以实现这一点。此外,玻璃在通信波长下的透明性使得能够将波导嵌入堆叠的玻璃结构中,用于6G应用。并且超薄(<100µm)玻璃可以很容易地制造出700 x 700mm的大尺寸。

玻璃——通常是硼硅酸盐玻璃或石英玻璃——用途也非常灵活。它可用作载体、嵌入元器件的芯基板、3D堆叠材料,或用于传感器和MEMS的气密封装腔体。玻璃的导热性优于有机材料,因此能更有效地将热量从有源器件上传导出去。其热膨胀系数(CTE)可以在3至10 ppm/°C之间调整,使其在低端与硅更兼容,或在高端与PCB更兼容。

玻璃在高频应用中也表现出色。其介电常数远低于硅(2.8 vs. 12),且具有低损耗角正切值,传输损耗比硅低几个数量级,大大提高了信号完整性。

多年来,由于其诸多好处,玻璃作为下一代封装基板材料日益受到业界关注。其一个关键特性是能够实现高互连密度和低于2µm的RDL特征尺寸。“过去两年人工智能计算的激增凸显了一点,即为了提高SiP内的通信速度而需要浓缩布线密度,这已成为IC封装研发的焦点,”Disco Hi-Tec America的技术经理Frank Wei说道。

然而,它并非完美无缺。玻璃的切割(分割)很难不产生微裂纹,并且大规模、可重复地制造数千个精细间距的玻璃通孔(TGV)的挑战阻碍了玻璃发挥其全部潜力。英特尔在过去10年里对玻璃基板进行了大量投资,并在本月早些时候确认仍在推进玻璃基板项目。尽管存在制造障碍,但改进HPC/AI芯片质量的承诺正在推动其快速发展,这在2025年电子元件与技术会议(ECTC)及其他近期会议上得到了证明,研究人员展示了在以下方面的进展:

- 用于>100 GHz数据速率的堆叠玻璃;

- 通过激光改性和氢氟酸(HF)蚀刻实现TGV蚀刻;

- 无需后续蚀刻的直接激光蚀刻;

- 制造6µm、深宽比>15的TGV;

- 预测性良率建模以优化套刻精度,加速面板级扇出封装(FOPLP)良率提升;

- 在分割界面处逐渐减薄积层以防止玻璃破裂。

堆叠玻璃用于高频应用

玻璃是6G无线通信网络的理想选择,因其高频传输损耗极低,必须支持>100 GHz的数据速率。在堆叠玻璃中进行异质集成可以将高频前端芯片与低损耗互连集成到大规模天线阵列中。

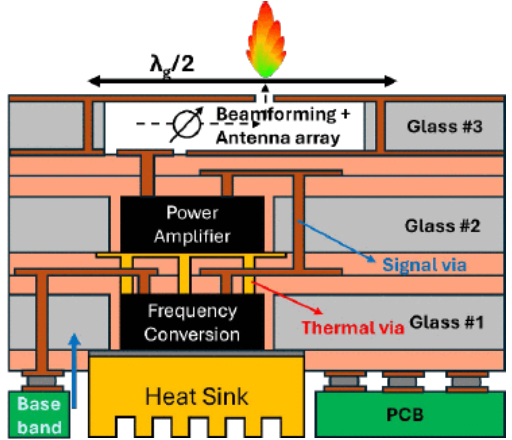

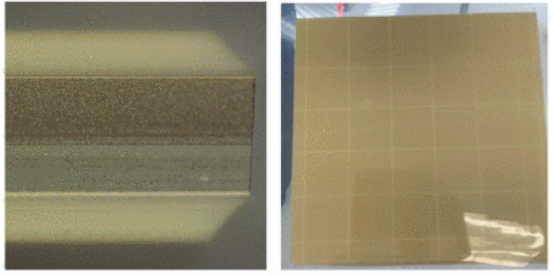

“通过将收发器模块分解为单个功能芯片,例如功率放大器和频率转换器,这些芯片可以嵌入到堆叠的基板芯中并垂直互连,”佐治亚理工学院的博士生Xingchen Li说。[1] 在玻璃基板中堆叠2英寸(50 x 50mm)芯片的工艺亮点包括菊花链结构的集成、玻璃层之间的良好对准(3µm)、玻璃激光钻孔和铜填充。

研究人员选择了一种ABF(味之素积层膜,Dk = 3.3, Df = 0.0044)同时作为低介电常数介质和玻璃粘合剂,并在两个层级上采用基于RDL的共面波导(见图1)。宽带电性能达到220 GHz,损耗仅为0.3 dB。

图1:堆叠玻璃架构使用未固化的ABF介质作为粘合剂,采用激光钻孔和化学镀铜种子层/电镀填充。来源:ECTC [1]

100 µm厚的玻璃面板通过倒装芯片键合到未固化的ABF上进行堆叠,这最大限度地减少了加热时的面板移位。ABF封装芯片后,在顶部玻璃上再层压另一层未固化的ABF(15µm)并进行固化。使用激光加工形成用于信号传输和热改善的玻璃通孔,随后使用促进粘合剂、化学镀铜和电镀来填充高达130µm、节距100 µm的V形通孔。该方法显示出作为6G应用3D堆叠方法的潜力。

玻璃通孔(TGV)工艺

激光在制造TGV中起着关键作用。LPKF Laser & Electronics的战略产品经理Richard Noack最近详细介绍了如何改进激光诱导深度蚀刻(LIDE)技术以用于生产级应用。[2] LIDE首先对硼硅酸盐玻璃进行激光改性,改变其结构,使其易于进行各向异性蚀刻。

激光改性过程使用单个激光脉冲破坏玻璃的组成。“初始改性的宽度小于1µm,可以描述为‘一串气泡’,”Noack说。“沿着这种轻微改性的蚀刻速率比材料其余部分高100倍。”

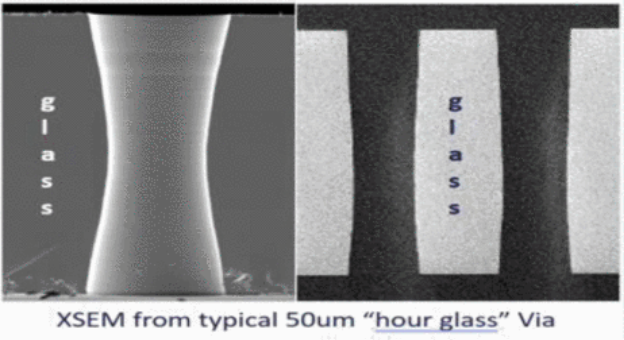

接下来,在氢氟酸(HF)中进行湿法蚀刻以形成所需的形状(见图2)。LIDE已证明能够蚀刻小至3µm、间距5µm的玻璃通孔。

为了便于面板湿法处理,Yield Engineering Systems (YES) 开发了一种自动化的多腔室浸泡、冲洗和干燥设备,可处理多达12片尺寸为510 x 515mm的玻璃面板。该公司的高级总监Venugopal Govindarajulu介绍了用于制造旨在用于大批量生产的高深宽比玻璃通孔的湿法蚀刻方法。[3]

该设备使用商用玻璃材料,在130°C下可以高达80µm/小时的蚀刻速率蚀刻25-100µm的TGV。可以调整激光工艺以实现所需的形状——圆柱形、沙漏形、直通孔或空腔。

YES团队确定蚀刻速率和TGV轮廓是HF槽液化学性质、酸浓度和蚀刻温度的函数,可以通过调整这些参数来实现5:1的高选择性蚀刻(改性区域蚀刻速率/未处理玻璃蚀刻速率)。

沙漏状形状被认为最适合使用铜PVD实现无空洞填充。湿法蚀刻槽实现的深宽比(深度/直径)范围从4:1到20:1(200µm厚玻璃)。“在大批量制造环境中,关键的考虑因素是实现更高蚀刻速率的最佳化学配方、优化流体动力学以实现均匀蚀刻,以及良好的温度和流量控制以实现工艺能力,”Govindarajulu说。

图2:沙漏形轮廓最兼容于铜PVD种子层及随后的电镀。来源:ECTC [3]

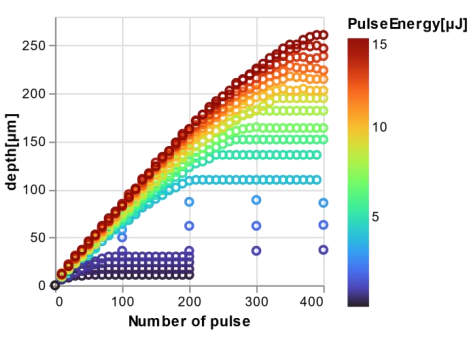

尽管LIDE被认为是玻璃通孔的主导工艺,但各公司正在探索不涉及有毒HF的更环保的解决方案。东京大学的Toshi Otsu及其同事能够在100µm厚的旭硝子ENA1材料中制造出6µm宽、节距25µm的孔。[4] 该方法使用不同脉冲能量和脉冲次数的深紫外激光(257nm)准直光束。“使用超短脉冲激光最大限度地减少了对周围材料的热影响,从而实现精确和洁净的加工,”作者说。

图3:孔深随脉冲能量增加但存在极限。来源:ECTC [4]

SEM横截面显示高深宽比TGV在玻璃顶部的孔径比底部大。深度最大可达260µm,深宽比在20:1至25:1之间(见图3)。未来的工作将研究改变激光的数值孔径如何影响孔径。

玻璃芯基板从研发到良率提升

每当业界考虑使用玻璃等新材料时,模拟仿真可以提供材料间相互作用的 insights。它也有助于比较工艺,例如哪种促进粘合剂与玻璃的界面最好,或者PVD铜还是化学镀铜能形成更好的种子层。

“当转向玻璃这类新型基板时,原子级建模将成为预测在玻璃基板上放置多个薄膜时形成的界面行为的关键工具。这甚至在开始制造之前,就为应该集中精力在哪里以及加工中需要注意什么提供了方向,”Synopsys的首席解决方案工程师Anders Blom说。

因为玻璃是非晶材料,必须使用数十个原子进行建模,而像晶体硅这样的材料只需要2个原子就可以开始建模。“GPU加速和机器学习算法的最新进展现在使我们能够结合使用快速力场和精确的第一性原理建模来构建和运行这种复杂系统的真实模型,”Blom指出。

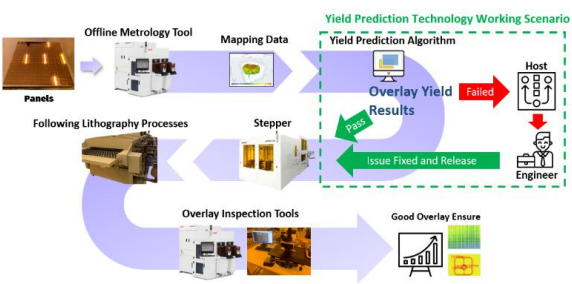

另一种有助于推动研发和面板级良率提升的工具是预测性良率建模,尤其对于带有HBM的AI处理器。Onto Innovation的应用开发经理John Chang在ECTC上详细介绍了一种预测性良率模型,特别关注套刻缺陷。“这些组件很昂贵,”他说。“因此,在每一步最大化良率并及早识别缺陷以最小化损失至关重要。”

尽管玻璃芯基板相对于有机芯基板显著减少了图形失真和翘曲,但它们的存在仍然会影响面板级扇出封装(FOPLP)的良率。Onto Innovation的方法使用离线计量工具测量芯片移位和失真,然后将其与定制化的工艺参数和机器学习算法相结合,以快速减少510 x 515mm面板上的套刻缺陷。[5] “通过利用预测分析和机器学习模型,良率预测技术不仅能够识别潜在的在线工艺缺陷,还能在早期推荐可行的解决方案以优化生产参数,从而实现更快的产能提升,”Chang说。

面板级套刻误差通常在整个面板上呈现非线性模式,有四种可能的校正方法——全局校正、基于区域(例如,每面板4个区域)的校正、基于芯片的校正和逐点校正。基于芯片的校正产生最高的良率,但校正时间拖累了吞吐量。相反,对于每个面板,基于点的校正在具有相似移位的区域中每次曝光处理多个芯片,从而在吞吐量上妥协较少的情况下保持高良率。然而,仅此优化提供的良率仍低于可接受水平。

图4:良率预测工作流程能够实时监控和分析影响套刻良率的芯片移位和图形失真。来源:ECTC [5]

为了加速套刻精度的改进进程,该团队建立了一种模拟最终良率与不同工艺参数条件函数关系的方法。"通过利用这项技术(图4完整流程),用户可通过仿真识别最优参数,并通过运行认证基板来验证预测结果,"Chang表示。

此外,图表和直方图有助于在生产型FOPLP环境中早期识别套刻问题,从而加速认证流程并简化工艺优化。"随着FOPLP技术在未来几年的预期显著增长,我们相信良率预测技术将为实现FOPLP光刻的快速量产和高良率提供清晰路径,"Chang强调。

防止SeWaRe缺陷

玻璃的脆性众所周知。微裂纹是在操作处理尤其是切割过程中的主要顾虑。

玻璃芯基板切割时出现的故障被称为SeWaRe(源自日语"背割れ"意指背面开裂)。Disco公司的Frank Wei与Andrew Frederick通过研究不同厚度(125、200和500μm)的裸硼硅酸盐玻璃,以及在玻璃两侧层压两种不同类型积层结构的情况,深入探究了基板切割开裂的成因,最终提出了最小化损伤的最佳实践方案。[6]

Disco研究表明,双刀片切割方式相比激光切割技术(激光隐形切割与激光增强烧蚀填充)会产生更多边缘崩缺,但能获得更光滑的切面。切割芯片尺寸为5×5mm和15×15mm。重要的是,层压积层结构能增强芯片强度,且采用高模量介质材料时可获得最佳芯片强度。

有限元建模(FEM)显示边缘崩缺始于最尖锐的微观缺陷处——这些点在切割过程中应力最为集中。Disco团队发现当层压积层延伸至切割区域边缘时,会出现SeWaRe缺陷。通过部分去除切割边缘的层压积层(称为回切法),可有效消除这类缺陷。

图5:当对聚合物积层(正面与背面)采用回切法后,切割过程中的崩缺现象完全消除。来源:ECTC [6]

虽然主流玻璃面板切割工艺通常在基板两侧完成积层压合后进行,但索尼半导体解决方案的Shun Mitarai团队开创性地提出将切割后的基板嵌入有机树脂中以实现边缘保护的新方法。[7] 他们将分割式玻璃芯嵌入工艺(SGEP)与行业传统工艺进行对比:"传统工艺(CP)在保持大尺寸玻璃面板状态下制造玻璃芯基板虽然流程直接,但需要巨额投资用于双面互连形成,并需大量设备改造来避免玻璃破损。"

传统工艺先进行TGV蚀刻与金属化,接着完成核心互连工艺,然后层压积层并进行切割,最后在基板各边缘涂覆有机树脂。

而SGEP工艺在核心互连形成后即切割基板。这个创新步骤将玻璃芯片段嵌入覆铜层压板框架中,随后层压积层并切割树脂框架。

Mitarai指出这种对单个玻璃边缘的保护工艺较为复杂。双面积层能有效平衡单面处理导致的CTE引起的翘曲,而分割式玻璃芯嵌入工艺则支持单面处理并提供更优异的基板保护。该方法的后续改进将致力于提升工艺与严格设计规则的兼容性,并进一步提高良率。

玻璃芯混合键合

玻璃的平整度与位置精度创造了新的集成与工艺可能性。"与有机芯基板不同,玻璃芯基板具有足够平整度来实现铜-铜混合键合,"欣兴电子高级特助刘汉诚博士表示。[8] 他强调玻璃并非有机芯基板的替代品,而是对现有材料的补充——因为采用二氧化硅介质和双大马士革工艺可制造更精细的RDL线宽线距。

欣兴团队演示了器件在有机芯与玻璃芯基板上的倒装芯片键合。他们发现玻璃基板上倒装芯片混合键合的翘曲略大于倒装芯片微凸块连接,但两者均在可接受范围内。他们将微凸块的低翘曲性归因于其减震器作用。研究者建议当与CTE为18 ppm/°C的PCB键合时,宜采用较高CTE的玻璃(10 ppm/°C)。

结论

玻璃生态圈企业正取得重大进展,以应对多芯片先进封装中芯片与基板尺寸持续增大的趋势。激光改性结合HF蚀刻是目前形成不同形状尺寸玻璃通孔的主流方法,但若准分子激光直接蚀刻能实现后续铜填充所需的通孔形状,将成为更环保的选择。

切割过程中产生的玻璃微崩缺(SeWaRe)若能在刀片或激光切割前实施一致的聚合物回切处理则可有效预防。尽管切换切割方法可减少微裂纹,但尚不能完全消除。

- 收藏